The 3D-MAPS Processors

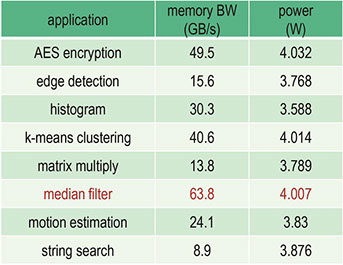

3D-MAPS V1 supports 42 instructions, and we wrote 8 parallel applications and ran them on our chip. Here are the memory bandwidth and power measurement results.

The theoretical maximum memory bandwidth 3D-MAPS V1 can achieve is 70.9GB/s, which is computed by 277MHz x 64 (cores) x 4 Bytes (1 word). One of our applications, median filter, got very close to this theoretical value at the lowest power consumption. As a comparison, here are the maximum achievable bandwidth values of the state-of-the-art processor and memory technology (as of Sep 2011):

??Intel i7 Extreme Edition + Samsung DDR3 1600 MHz = 1600 MHz x 2 ch x 8 Bytes = 25.6 GB/s

??Intel Xeon E7 + Samsung DDR3 1066 MHz = 1066 MHz x 4 ch x 8 Bytes = 34.1 GB/s

3D-MAPS V1 is fabricated in 130nm technology in 5mm x 5mm footprint. If 3D-MAPS V1 is fabricated in 45nm in 15mm x 15mm footprint (as in Intel i7), the maximum memory bandwidth skyrockets as follows: ??277 MHz X 5 (speedup from 45nm) x 64 ch x 9 (more area) x 4 (smaller cores) x 4 Bytes = 12,764 GB/s

This truly demonstrates the enormous memory bandwidth benefit of core+memory 3D IC.

School of Electrical and Computer Engineering

Georgia Institute of Technology

777 Atlantic Drive NW

Atlanta, GA 30332-0250, USA

Office: KACB #2360

Phone: 404-894-0373

Email: limsk@ece.gatech.edu

http://users.ece.gatech.edu/limsk